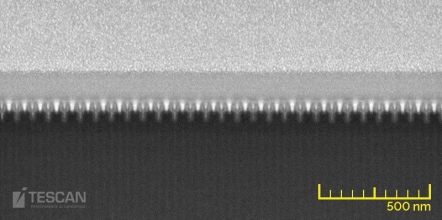

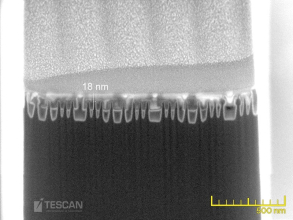

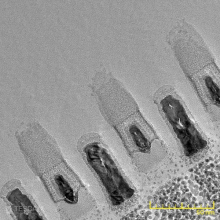

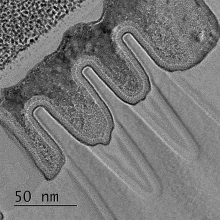

Ngành công nghiệp bán dẫn đã và đang thực hiện việc thu nhỏ kích thước của các thiết bị điện tử và các node dưới 20nm đã có sẵn. Các mạch tích hợp là các cấu trúc nhiều lớp có các thành phần chính là các bóng bán dẫn nhiều cổng, trong đó kênh source-drain (“fin”) được bao quanh bởi một cổng 3D.

Phân tích lỗi Mạch tích hợp IC

Chip, Vi mạch, IC (Mạch tích hợp)..., hoặc bất cứ cái gì bạn muốn gọi chúng, là một loại vi mạch điện tử, đã tạo ra sự tiến bộ của công nghệ với trình độ hiện tại. Nếu không có phát minh này, máy tính, viễn thông và các thiết bị điện và điện tử sẽ rất khác.

Kính hiển vi điện tử quét SEM TESCAN đóng vai trò vô cùng quan trọng trong việc phân tích lỗi sai của Mạch tích hợp; đồng thời, FIB-SEM hỗ trợ cho việc chuẩn bị mẫu một cách hoàn hảo để tiến hành chụp ảnh và phân tích trên TEM.

Quy trình phân tích lỗi của các Mạch tích hợp liên quan đến delayering (tách lớp). Cho đến nay, việc tách lớp được thực hiện bằng phương pháp khử cơ học. Tuy nhiên, đối với các thiết bị trong tương lai thì không thể sử dụng phương pháp này do sự biến dạng cơ tính và phản ứng hóa học.

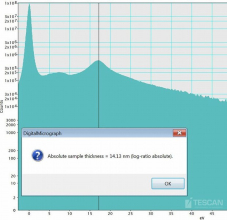

Hệ thống Kính hiển vi điện tử quét chùm ion hội tụ FIBSEM của TESCAN thực hiện hỗ trợ cho việc chuẩn bị mẫu để phân tích trên máy TEM.

Phân tích các lỗi trong mạch tích hợp có liên quan đến SEM thường gặp:

-

Delayering và electrical probing trong công nghệ nodes của thế hệ trước

-

Chuẩn bị mẫu TEM cho các mạch tích hợp

-

Phân tích cấu trúc 3D (dựng lại cấu trúc 3D BSE) với FIB-SEM hỗ trợ thực hiện chụp cắt lớp.

-

Kỹ thuật EBIC (Electron Beam Induced Current), EBAC (Electron Beam Absorbed Current)

-

Thực hiện chụp/nghiên cứu SEM ở điện áp thấp

Hình ảnh ứng dụng trong lĩnh vực Phân tích lỗi Mạch tích hợp IC